FPGA-basierte Signal

Eine Hochleistungs-Digitalsignalverarbeitungsplattform auf Basis der Lattice-FPGA-Architektur für Echtzeit-Datenerfassung, -filterung und -spektralanalyse bei GHz-Geschwindigkeiten.

Eine Hochleistungs-Digitalsignalverarbeitungsplattform auf Basis der Lattice-FPGA-Architektur für Echtzeit-Datenerfassung, -filterung und -spektralanalyse bei GHz-Geschwindigkeiten.

16-Kanal-ADC-Frontend mit Antialiasing-Filtern und programmierbaren Verstärkern

Lattice ECP5 mit Pipeline-DSP-Blöcken und benutzerdefinierten VHDL-IP-Kernen

FIR/IIR-Filter, FFT-Engine und digitaler Downconverter mit konfigurierbaren Parametern

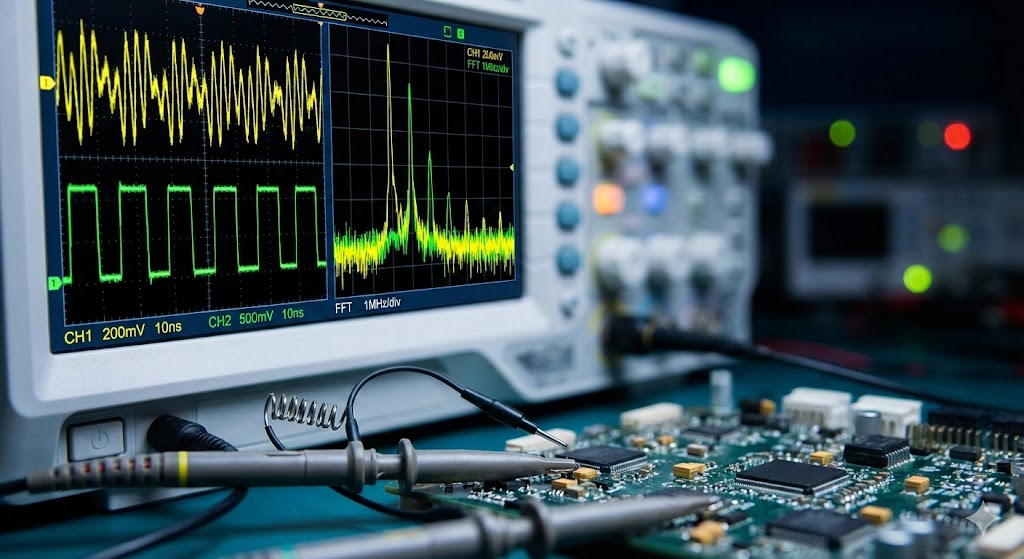

Echtzeit-Spektralanzeige mit Datenprotokollierung und Frequenzbereichs-Visualisierung

Parallele Pipeline-Architektur mit 2,4 GHz effektivem Durchsatz und deterministischer Latenz unter 10 Nanosekunden.

Zur Laufzeit programmierbare FIR- und IIR-Filterkoeffizienten für Bandpass-, Tiefpass-, Hochpass- und Kerbkonfigurationen.

Hardwarebeschleunigte 4096-Punkt-FFT mit Fensterfunktionen für Live-Spektralanalyse und Frequenzmessung.

Phasengekoppelte Abtastung über alle 16 ADC-Kanäle mit Sub-Nanosekunden-Synchronisationsgenauigkeit.

DDR3-Puffer mit 2 GB kontinuierlicher Signalerfassung mit Ringpuffer und getriggertem Erfassungsmodus.

SPI-, UART- und Gigabit-Ethernet-Schnittstellen für Konfiguration, Steuerung und Hochgeschwindigkeitsdatenübertragung.

Systemspezifikation der DSP-Pipeline, Datenflusseanalyse und FPGA-Ressourcenschätzung mit Yosys + nextpnr.

VHDL-Codierung benutzerdefinierter IP-Kerne einschließlich FIR-Filter, FFT-Engine und ADC-Schnittstellencontroller.

6-lagige Leiterplatte mit kontrollierten Impedanzleiterbahnen, Stromintegrationsanalyse und Hochgeschwindigkeitssignalführung.

GHDL + GTKWave Verhaltens- und Zeitsimulation mit Testbenches für alle Betriebsmodi.

Onboard-Tests mit kalibrierten Signalquellen zur Messung von SNR, THD und Verarbeitungslatenz.

Von Hochgeschwindigkeits-Signalverarbeitung bis hin zu individuellem Digitaldesign liefert unser Team FPGA-basierte Lösungen für maximale Leistung und Zuverlässigkeit.