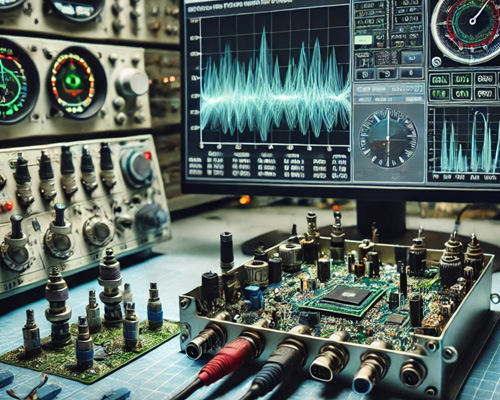

アンチエイリアスフィルタおよびプログラマブルゲインアンプを備えた16チャネルADCフロントエンド

カスタムVHDL IPコアを使用してパイプライン化されたDSPブロックを実行するLattice ECP5

設定可能なパラメータを備えたFIR/IIRフィルタ、FFTエンジン、およびデジタルダウンコンバータ

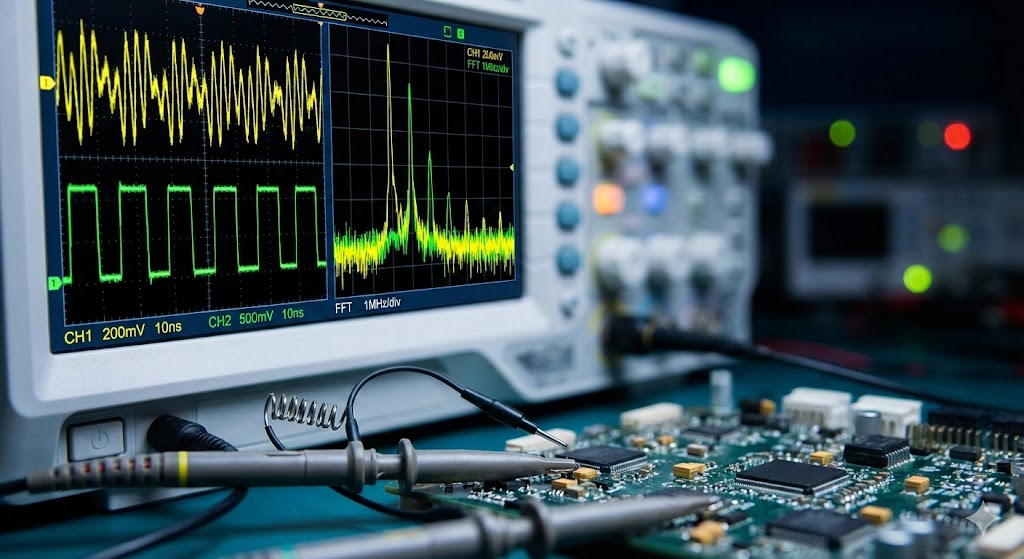

データロギングおよび周波数ドメイン視覚化を備えたリアルタイムスペクトルディスプレイ

10ナノ秒未満の確定的な遅延で2.4 GHzの効果的なスループットを達成する並列パイプラインアーキテクチャ。

バンドパス、ローパス、ハイパス、およびノッチ構成をサポートするランタイムプログラム可能なFIRおよびIIRフィルタ係数。

ライブスペクトル分析および周波数測定のためのウィンドウ関数を備えたハードウェアアクセラレーション4096ポイントFFT。

サブナノ秒の同期精度を備えた、全16のADCチャネルにわたるフェーズロックサンプリング。

循環バッファおよびトリガー取得モードを備えた2GBの連続信号キャプチャをサポートするDDR3バッファ。

構成、制御、およびホストシステムへの高速データ転送のためのSPI、UART、およびギガビットイーサネットインターフェイス。

DSPパイプラインのシステムレベルの仕様、データフロー分析、およびYosys + nextpnrを使用したFPGAリソースの見積もり。

FIRフィルタ、FFTエンジン、ADCインターフェースコントローラーを含むカスタムIPコアのVHDLコーディング。

制御されたインピーダンス配線、電源インテグリティ分析、および高速信号ルーティングを備えた6層PCB。

すべての動作モードをカバーするテストベンチを備えた、GHDL + GTKWaveの動作およびタイミングシミュレーション。

キャリブレーションされた信号源を使用したオンボードテスト、SNR、THD、および処理遅延の測定。