FPGA 기반 신호

GHz 속도에서의 실시간 데이터 수집, 필터링 및 스펙트럼 분석을 위해 Lattice FPGA 아키텍처에 구축된 고성능 디지털 신호 처리 플랫폼입니다.

GHz 속도에서의 실시간 데이터 수집, 필터링 및 스펙트럼 분석을 위해 Lattice FPGA 아키텍처에 구축된 고성능 디지털 신호 처리 플랫폼입니다.

안티앨리어싱 필터와 프로그래밍 가능한 이득 증폭기가 있는 16채널 ADC 프런트엔드

맞춤형 VHDL IP 코어로 파이프라인된 DSP 블록을 실행하는 Lattice ECP5

구성 가능한 매개변수가 있는 FIR/IIR 필터, FFT 엔진 및 디지털 다운컨버터

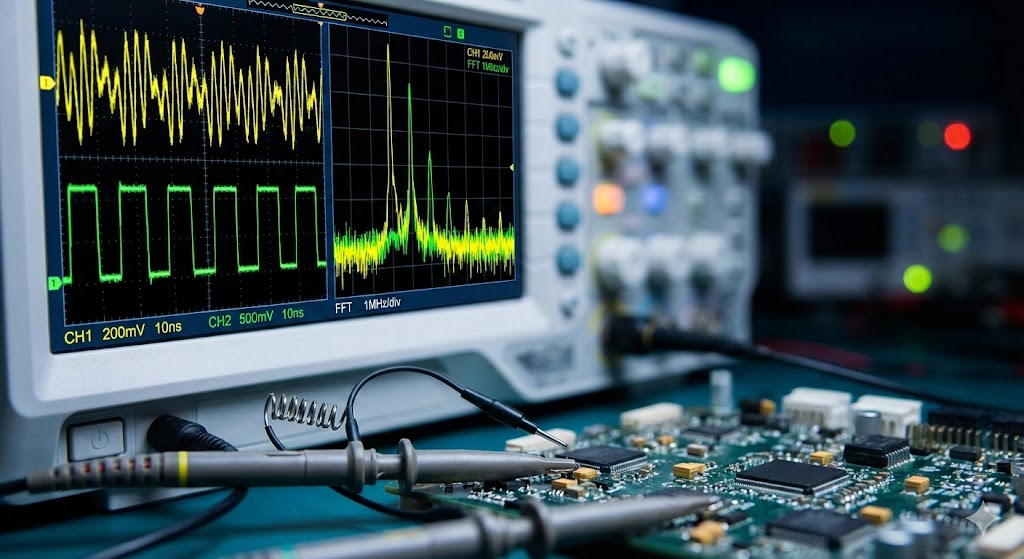

데이터 로깅 및 주파수 도메인 시각화를 통한 실시간 스펙트럼 디스플레이

10나노초 미만의 결정론적 지연 시간으로 2.4GHz의 유효 처리량을 달성하는 병렬 파이프라인 아키텍처.

대역 통과, 저역 통과, 고역 통과 및 노치 구성을 지원하는 런타임 프로그래밍 가능 FIR 및 IIR 필터 계수.

라이브 스펙트럼 분석 및 주파수 측정을 위한 창 함수가 포함된 하드웨어 가속 4096 포인트 FFT.

서브 나노초 동기화 정확도로 모든 16개 ADC 채널에 걸쳐 위상 고정 샘플링 수행.

순환 버퍼 및 트리거된 수집 모드로 2GB의 연속 신호 캡처를 지원하는 DDR3 버퍼.

호스트 시스템으로의 구성, 제어 및 고속 데이터 전송을 위한 SPI, UART 및 기가비트 이더넷 인터페이스.

Yosys + nextpnr을 사용한 DSP 파이프라인의 시스템 수준 사양 정의, 데이터 흐름 분석 및 FPGA 리소스 추정.

FIR 필터, FFT 엔진 및 ADC 인터페이스 컨트롤러를 포함한 맞춤형 IP 코어의 VHDL 코딩.

임피던스 제어 트레이스, 전력 무결성 분석 및 고속 신호 라우팅이 포함된 6레이어 PCB.

모든 작동 모드를 다루는 테스트 벤치가 있는 GHDL + GTKWave 동작 및 타이밍 시뮬레이션.

보정된 신호 소스를 사용한 온보드 테스트, SNR, THD 및 처리 대기 시간 측정.