Señal Basada en FPGA

Una plataforma de procesamiento digital de señales de alto rendimiento construida sobre arquitectura FPGA de Lattice para adquisición de datos en tiempo real, filtrado y análisis espectral a velocidades de GHz.

Una plataforma de procesamiento digital de señales de alto rendimiento construida sobre arquitectura FPGA de Lattice para adquisición de datos en tiempo real, filtrado y análisis espectral a velocidades de GHz.

Frontend ADC de 16 canales con filtros anti-aliasing y amplificadores de ganancia programables

Lattice ECP5 ejecutando bloques DSP en pipeline con núcleos IP VHDL personalizados

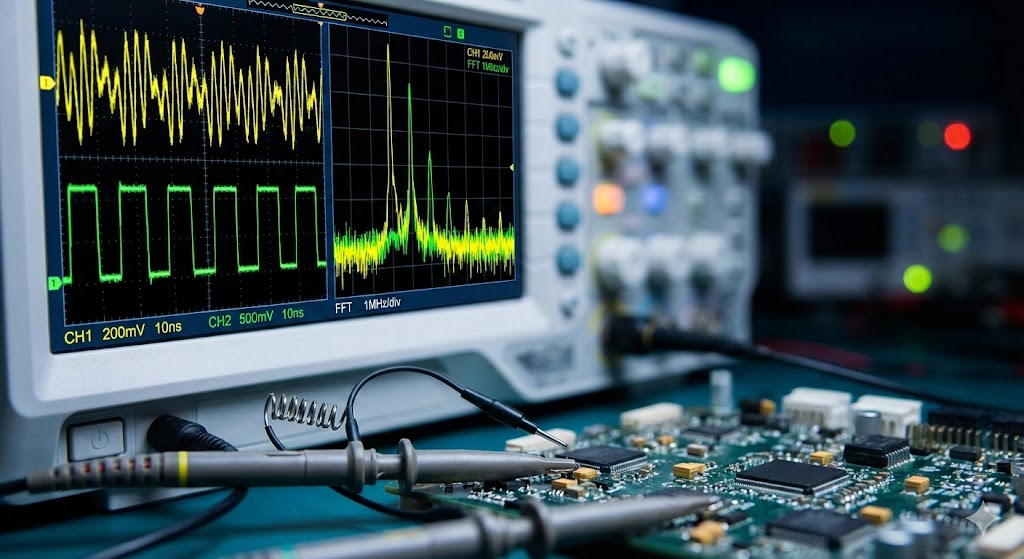

Filtros FIR/IIR, motor FFT y convertidor digital descendente con parámetros configurables

Visualización espectral en tiempo real con registro de datos y visualización en dominio de frecuencia

Arquitectura de pipeline paralelo que alcanza un rendimiento efectivo de 2.4 GHz con latencia determinista inferior a 10 nanosegundos.

Coeficientes de filtro FIR e IIR programables en tiempo de ejecución que soportan configuraciones de paso de banda, paso bajo, paso alto y rechazo de banda.

FFT acelerada por hardware de 4096 puntos con funciones de ventana para análisis espectral en vivo y medición de frecuencia.

Muestreo con bloqueo de fase en los 16 canales ADC con precisión de sincronización sub-nanosegundo.

Búfer DDR3 que soporta 2GB de captura continua de señal con modos de búfer circular y adquisición por disparo.

Interfaces SPI, UART y Gigabit Ethernet para configuración, control y transferencia de datos de alta velocidad a sistemas host.

Especificación a nivel de sistema del pipeline DSP, análisis de flujo de datos y estimación de recursos FPGA usando Yosys + nextpnr.

Codificación VHDL de núcleos IP personalizados incluyendo filtros FIR, motor FFT y controladores de interfaz ADC.

PCB de 6 capas con trazas de impedancia controlada, análisis de integridad de potencia y enrutamiento de señales de alta velocidad.

Simulación conductual y de temporización en GHDL + GTKWave con bancos de pruebas que cubren todos los modos operacionales.

Pruebas en tarjeta con fuentes de señal calibradas, midiendo SNR, THD y latencia de procesamiento.

Desde procesamiento de señales de alta velocidad hasta diseño digital personalizado, nuestro equipo ofrece soluciones basadas en FPGA diseñadas para máximo rendimiento y confiabilidad.